# MOS & SPECIAL COS/MOS 2<sup>nd</sup> EDITION ISSUED MARCH 1981

# INTRODUCTION

This databook contains data sheets on the SGS-ATES range of products in MOS and COS/MOS technology.

The information on each product has been specially presented in order that the performance of the product can be readily evaluated within any required equipment design.

The databook also contains a summary of the processes available in SGS-ATES for the development and production of the products listed.

# **NUMERICAL INDEX**

| M054       11       M752       169         M055       11       M754       173         M082/A       15       M755       177         M083/A       15       M756       177         M086/A       15       M760/A       185         M089       19       M761/A       195         M090       27       M764/A       205         M091       35       M1024       215         M099       19       M1124       219         M106       43       M2102A       223         M108       51       M2102AL       223         M110       61       M2114       229         M120       73       M2316E       233         M142/A       79       M2716       237         M190       83       M4015       245         M191       35       M4027       251         M192       89       M4116       263         M193/A/C/D       95       M5156       279         M258       109       M22100       303         M259       109       M36000       307         M269       117       M706                                                                                                                                                                  | Туре       | Page | Туре    | Page |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------|---------|------|

| M082/A       15       M755       177         M083/A       15       M756       177         M086/A       15       M760/A       185         M089       19       M761/A       195         M090       27       M764/A       205         M091       35       M1024       215         M099       19       M1124       219         M106       43       M2102A       223         M108       51       M2102A       223         M110       61       M2114       229         M120       73       M2316E       233         M142/A       79       M2316E       233         M190       83       M4015       245         M191       35       M4027       251         M192       89       M4116       263         M193/A/C/D       95       M5156       279         M208       51       M5912       291         M258       109       M22100       303         M259       109       M36000       307         M268       117       M274-XCARD       135         M714       139       M740 <td>M054</td> <td>11</td> <td>M752</td> <td>169</td>                                                                                                     | M054       | 11   | M752    | 169  |

| M083/A       15       M756       177         M086/A       15       M760/A       185         M089       19       M761/A       195         M090       27       M764/A       205         M091       35       M1024       215         M099       19       M1124       219         M106       43       M2102A       223         M108       51       M2102AL       223         M110       61       M2114       229         M120       73       M2316E       233         M142/A       79       M2716       237         M190       83       M4015       245         M191       35       M4015       245         M192       89       M4116       263         M193/A/C/D       95       M5156       279         M208       51       M5912       291         M258       109       M2100       303         M259       109       M36000       307         M268       117       M706       135         M714       139       M730       143         M731       147       M740                                                                                                                                                                  | M055       | 11   | M754    | 173  |

| MO86/A       15       M760/A       185         M089       19       M761/A       195         M090       27       M764/A       205         M091       35       M1024       215         M099       19       M1124       219         M106       43       M2102A       223         M108       51       M2102A       223         M110       61       M2114       229         M120       73       M2316E       233         M142/A       79       M2716       237         M190       83       M4015       245         M191       35       M4027       251         M192       89       M4116       263         M193/A/C/D       95       M5156       279         M208       51       M5912       291         M258       109       M22100       303         M259       109       M36000       307         M268       117       M706       135         M714       139       M730       143         M731       147       M740       151         M741       151       M747                                                                                                                                                                   | M082/A     | 15   | M755    | 177  |

| M089       19       M761/A       195         M090       27       M764/A       205         M091       35       M1024       215         M099       19       M1124       219         M106       43       M2102A       223         M108       51       M2102AL       223         M110       61       M2114       229         M120       73       M2316E       233         M142/A       79       M2716       237         M190       83       M4015       245         M191       35       M4027       251         M192       89       M4116       263         M193/A/C/D       95       M5156       279         M208       51       M5912       291         M258       109       M22100       303         M259       109       M36000       307         M268       117       M274-XCARD       125         M706       135       M714       139         M730       143       M731       147         M740       151       M740       151         M741       151       M740                                                                                                                                                               | M083/A     | 15   | M756    | 177  |

| M090       27       M764/A       205         M091       35       M1024       215         M099       19       M1124       219         M106       43       M2102A       223         M108       51       M2102AL       223         M110       61       M2114       229         M120       73       M2316E       233         M142/A       79       M2716       237         M190       83       M4015       245         M191       35       M4027       251         M192       89       M4116       263         M193/A/C/D       95       M5156       279         M208       51       M5912       291         M258       109       M22100       303         M259       109       M36000       307         M268       117       M274-XCARD       125         M706       135       M714       139         M730       143       M731       147         M740       151       M740       151         M741       151       M740       151         M747       155       M56                                                                                                                                                                 | M086/A     | 15   | M760/A  | 185  |

| M091       35       M1024       215         M099       19       M1124       219         M106       43       M2102A       223         M108       51       M2102AL       223         M110       61       M2114       229         M120       73       M2316E       233         M142/A       79       M2716       237         M190       83       M4015       245         M191       35       M4027       251         M192       89       M4116       263         M193/A/C/D       95       M5156       279         M208       51       M5912       291         M258       109       M22100       303         M259       109       M36000       307         M268       117       M274-XCARD       125         M702       131       M706       135         M714       139       M730       143         M738       151       M740       151         M740       151       M747       151         M747       151       M747       155                                                                                                                                                                                                   | M089       | 19   | M761/A  | 195  |

| M099       19       M1124       219         M106       43       M2102A       223         M108       51       M2102AL       223         M110       61       M2114       229         M120       73       M2316E       23         M142/A       79       M2716       237         M190       83       M4015       245         M191       35       M4027       251         M192       89       M4116       263         M193/A/C/D       95       M5156       279         M208       51       M5912       291         M258       109       M22100       303         M259       109       M36000       307         M268       117       M274-XCARD       125         M702       131       M706       135         M714       139       M730       143         M738       151       M740       151         M740       151       M740       151         M747       151       M747       151         M750       155       M5156       150                                                                                                                                                                                                   | M090       | 27   | M764/A  | 205  |

| M106       43       M2102A       223         M108       51       M2102AL       223         M110       61       M2114       229         M120       73       M2316E       233         M142/A       79       M2716       237         M190       83       M4015       245         M191       35       M4027       251         M192       89       M4116       263         M193/A/C/D       95       M5156       279         M208       51       M5912       291         M258       109       M22100       303         M259       109       M36000       307         M268       117       M269       117         M702       131       M706       135         M714       139       M730       143         M730       143       M731       147         M738       151       M740       151         M740       151       M747       151         M750       155       M5000       300                                                                                                                                                                                                                                                    | M091       | 35   | M1024   | 215  |

| M108       51       M2102AL       223         M110       61       M2114       229         M120       73       M2316E       233         M142/A       79       M2716       237         M190       83       M4015       245         M191       35       M4027       251         M192       89       M4116       263         M193/A/C/D       95       M5156       279         M208       51       M5912       291         M258       109       M22100       303         M259       109       M36000       307         M268       117       M706       135         M702       131       M706       135         M714       139       M730       143         M730       143       M731       147         M738       151       M740       151         M741       151       M747       151         M750       155       M55       Section of the property of the proper | M099       | 19   | M1124   | 219  |

| M110       61       M2114       229         M120       73       M2316E       233         M142/A       79       M2716       237         M190       83       M4015       245         M191       35       M4027       251         M192       89       M4116       263         M193/A/C/D       95       M5156       279         M208       51       M5912       291         M258       109       M22100       303         M259       109       M36000       307         M268       117       M769       117         M274-XCARD       125       M706       135         M714       139       M730       143         M730       143       M730       143         M740       151       M740       151         M747       151       M747       151         M750       155       M55       W114                                                                                                                                                                                                                                                                                                                                          | M106       | 43   | M2102A  | 223  |

| M120       73       M2316E       233         M142/A       79       M2716       237         M190       83       M4015       245         M191       35       M4027       251         M192       89       M4116       263         M193/A/C/D       95       M5156       279         M208       51       M5912       291         M258       109       M22100       303         M259       109       M36000       307         M268       117       M36000       307         M269       117       M702       131         M700       135       M714       139         M730       143       M730       143         M731       147       M738       151         M740       151       M740       151         M747       151       M747       151         M750       155       H       155                                                                                                                                                                                                                                                                                                                                                 | M108       | 51   | M2102AL | 223  |

| M142/A       79       M2716       237         M190       83       M4015       245         M191       35       M4027       251         M192       89       M4116       263         M193/A/C/D       95       M5156       279         M208       51       M5912       291         M258       109       M22100       303         M259       109       M36000       307         M268       117       M269       117         M274-XCARD       125       M702       131         M706       135       M714       139         M730       143       M731       147         M738       151       M740       151         M741       151       M747       151         M750       155       H       155                                                                                                                                                                                                                                                                                                                                                                                                                                      | M110       | 61   | M2114   | 229  |

| M190       83       M4015       245         M191       35       M4027       251         M192       89       M4116       263         M193/A/C/D       95       M5156       279         M208       51       M5912       291         M258       109       M22100       303         M259       109       M36000       307         M268       117       M36000       307         M269       117       M702       131         M702       131       135         M714       139       43         M730       143       47         M738       151         M740       151         M741       151         M747       151         M750       155                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | M120       | 73   | M2316E  | 233  |

| M191       35       M4027       251         M192       89       M4116       263         M193/A/C/D       95       M5156       279         M208       51       M5912       291         M258       109       M22100       303         M259       109       M36000       307         M268       117       M36000       307         M269       117       M702       131         M702       131       39       300         M714       139       300       300         M730       143       300       300         M731       147       300       300         M740       151       300       300         M741       151       300       300         M747       151       300       300         M750       155       300       300         M200       303       300       300         M36000       300       300       300         M36000       300       300       300         M200       131       300       300         M700       143       300       300     <                                                                                                                                                                     | M142/A     | 79   | M2716   | 237  |

| M192       89       M4116       263         M193/A/C/D       95       M5156       279         M208       51       M5912       291         M258       109       M22100       303         M259       109       M36000       307         M268       117       M269       117         M274-XCARD       125       M702       131         M706       135       M714       139         M730       143       M731       147         M738       151       M740       151         M741       151       M747       151         M747       151       M747       151         M750       155       M4116       263         M4116       263       M5156       279         M5000       303       303       303         M6000       307       303       303         M702       131       400       400         M731       147       400       400         M747       151       400       400         M750       155       400       400                                                                                                                                                                                                          | M190       | 83   | M4015   | 245  |

| M193/A/C/D       95       M5156       279         M208       51       M5912       291         M258       109       M22100       303         M259       109       M36000       307         M268       117       M36000       307         M269       117       M702       131         M706       135       M714       139         M730       143       M731       147         M738       151       M740       151         M741       151       M747       151         M750       155       M5000       303         M5156       M6912       291         M22100       303       303         M36000       307       307                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | M191       | 35   | M4027   | 251  |

| M208     51     M5912     291       M258     109     M22100     303       M259     109     M36000     307       M268     117     M36000     307       M269     117     M702     131       M706     135     M714     139       M730     143     M731     147       M738     151     M740     151       M741     151     M747     151       M750     155     40     40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | M192       | 89   | M4116   | 263  |

| M258       109       M22100       303         M259       109       M36000       307         M268       117       M36000       307         M269       117       M274-XCARD       125         M702       131       M706       135         M714       139       M730       143         M731       147       M738       151         M740       151       M741       151         M747       151       M747       151         M750       155       M55       M2100       303         M36000       307       307       M36000       307                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | M193/A/C/D | 95   | M5156   |      |

| M259       109       M36000       307         M268       117       M269       117         M274-XCARD       125       M702       131         M706       135       M714       139         M730       143       M731       147         M738       151       M740       151         M741       151       M747       151         M750       155       M750       M750                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | M208       | 51   | M5912   |      |

| M268       117         M269       117         M274-XCARD       125         M702       131         M706       135         M714       139         M730       143         M731       147         M738       151         M740       151         M741       151         M747       151         M750       155                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | M258       | 109  | M22100  | 1    |

| M269       117         M274-XCARD       125         M702       131         M706       135         M714       139         M730       143         M731       147         M738       151         M740       151         M741       151         M747       151         M750       155                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | M259       | 109  | M36000  | 307  |

| M274-XCARD       125         M702       131         M706       135         M714       139         M730       143         M731       147         M738       151         M740       151         M741       151         M747       151         M750       155                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | M268       | 117  |         |      |

| M702     131       M706     135       M714     139       M730     143       M731     147       M738     151       M740     151       M741     151       M747     151       M750     155                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | M269       |      |         |      |

| M706     135       M714     139       M730     143       M731     147       M738     151       M740     151       M741     151       M747     151       M750     155                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | M274-XCARD | 125  |         |      |

| M714     139       M730     143       M731     147       M738     151       M740     151       M741     151       M747     151       M750     155                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | M702       |      |         |      |

| M730 143<br>M731 147<br>M738 151<br>M740 151<br>M741 151<br>M747 151<br>M750 155                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | M706       |      |         |      |

| M731 147 M738 151 M740 151 M741 151 M747 151 M750 155                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | M714       | 139  |         |      |

| M738 151<br>M740 151<br>M741 151<br>M747 151<br>M750 155                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | M730       |      |         |      |

| M740 151<br>M741 151<br>M747 151<br>M750 155                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | M731       |      |         |      |

| M741 151<br>M747 151<br>M750 155                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | M738       | 151  |         |      |

| M747 151<br>M750 155                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | M740       | 151  |         |      |

| M750 155                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | M741       | 151  |         |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | M747       | 151  |         |      |

| M751 159                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | M750       | 155  |         |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | M751       | 159  |         |      |

# **FUNCTIONAL INDEX**

| Type       | Technology    | Function                                             | Page |

|------------|---------------|------------------------------------------------------|------|

| MUSIC      |               |                                                      |      |

| M082/A     | N channel MOS | Tone generator                                       | 15   |

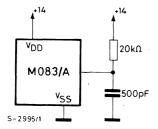

| M083/A     | N channel MOS | Tone generator                                       | 15   |

| M086/A     | N channel MOS | Tone generator                                       | 15   |

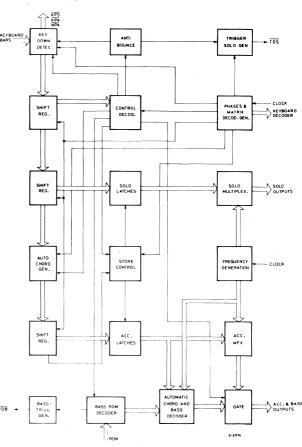

| M108       | N channel MOS | Single chip organ (solo + accompaniment)             | 51   |

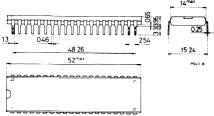

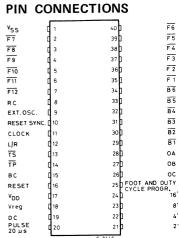

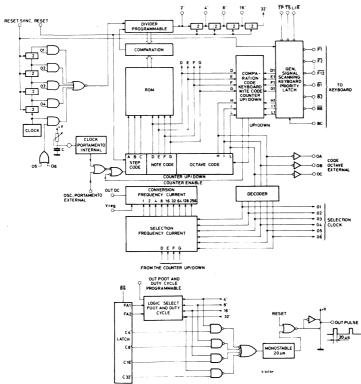

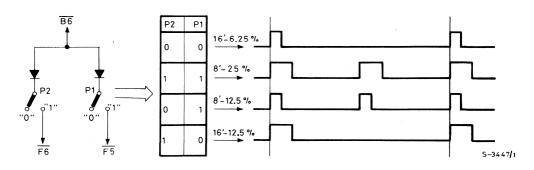

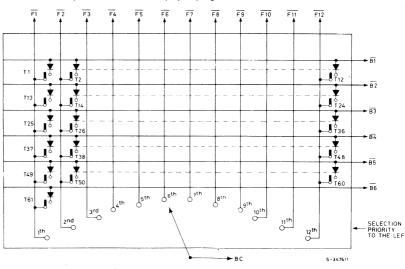

| M110       | N channel MOS | Monophonic synthesizer                               | 61   |

| M208       | N channel MOS | Single chip organ (solo + accompaniment)             | 51   |

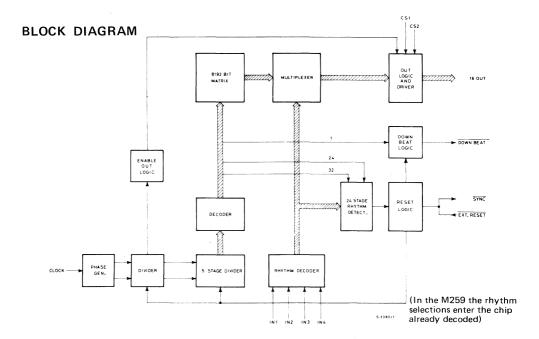

| M258       | N channel MOS | Rhythm generator                                     | 109  |

| M259       | N channel MOS | Rhythm generator                                     | 109  |

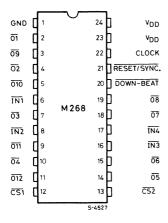

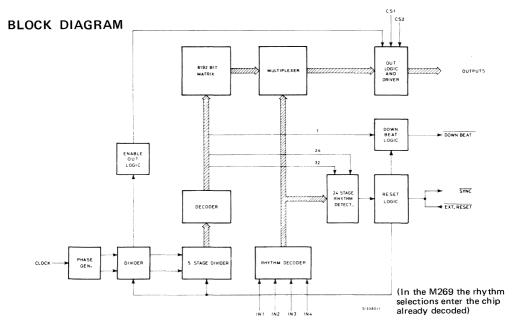

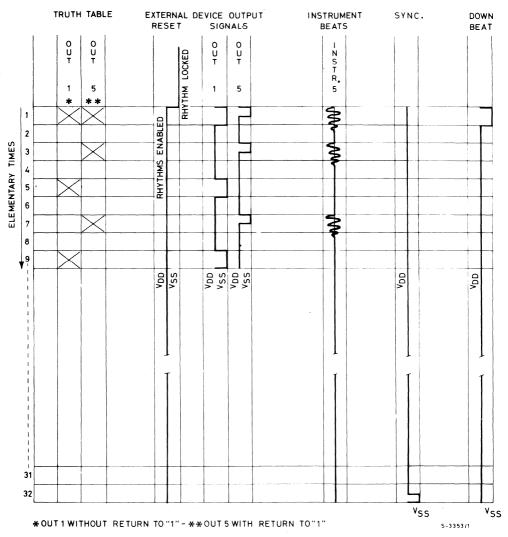

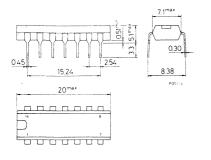

| M268       | N channel MOS | Rhythm generator                                     | 117  |

| M269       | N channel MOS | Rhythm generator                                     | 117  |

| M738       | COS/MOS       | 7-stage divider                                      | 151  |

| M740       | COS/MOS       | 7-stage divider                                      | 151  |

| M741       | COS/MOS       | 7-stage divider                                      | 151  |

| M747       | COS/MOS       | 7-stage divider                                      | 151  |

| TV & RADIO |               |                                                      |      |

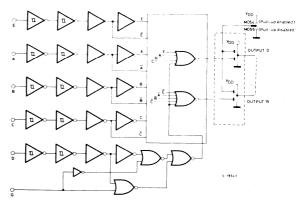

| M054       | N channel MOS | 1 of 16 decoder                                      | 11   |

| M055       | N channel MOS | 1 of 16 decoder                                      | 11   |

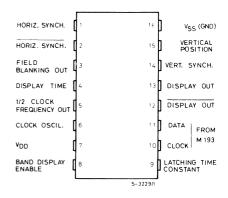

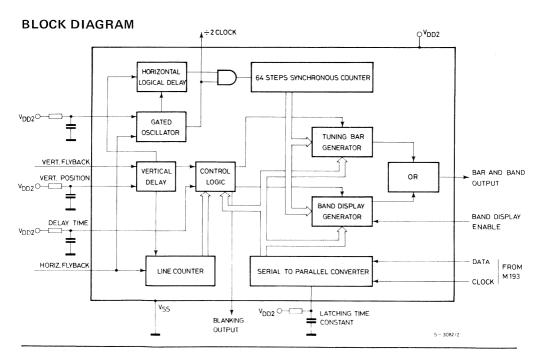

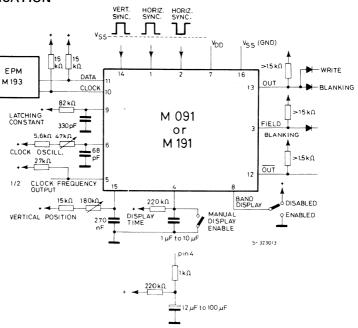

| M091       | N channel MOS | On-screen tuning scale and band display              | 27   |

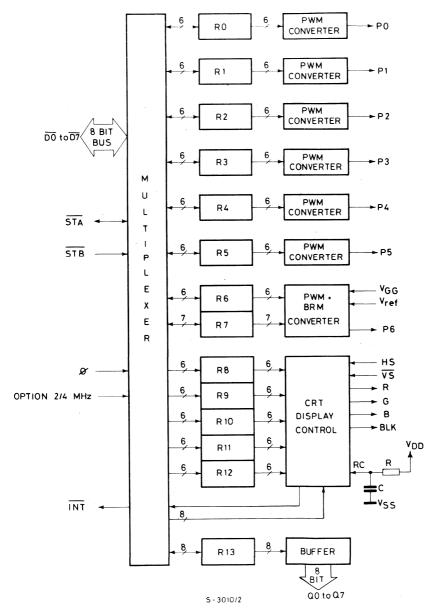

| M106       | N channel MOS | TV microprocessor interface                          | 43   |

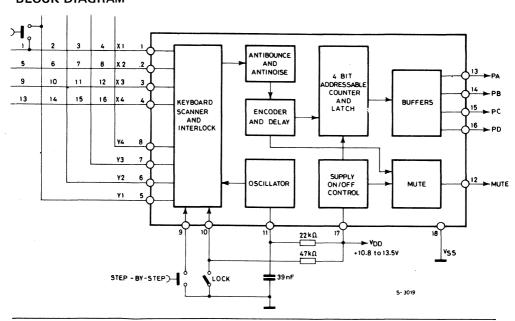

| M190       | N channel MOS | 16 key keyboard encoder and latch                    | 83   |

| M191       | N channel MOS | On-screen tuning scale and band display              | 35   |

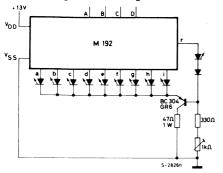

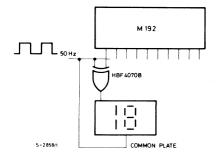

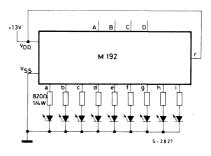

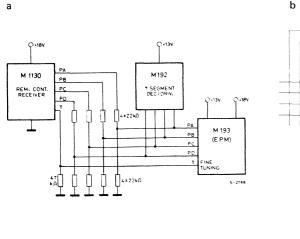

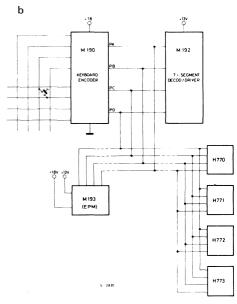

| M192       | COS/MOS       | 4-bit binary 7-segment decoder driver                | 89   |

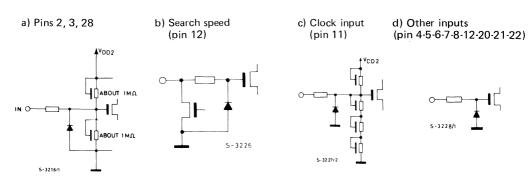

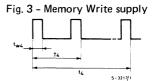

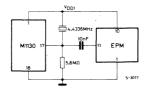

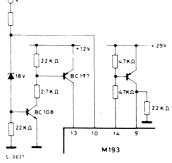

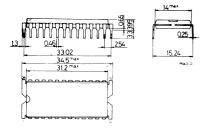

| M193A/C/D  | N channel MOS | EPM 16-Electronic Program memory (16 stations)       | 95   |

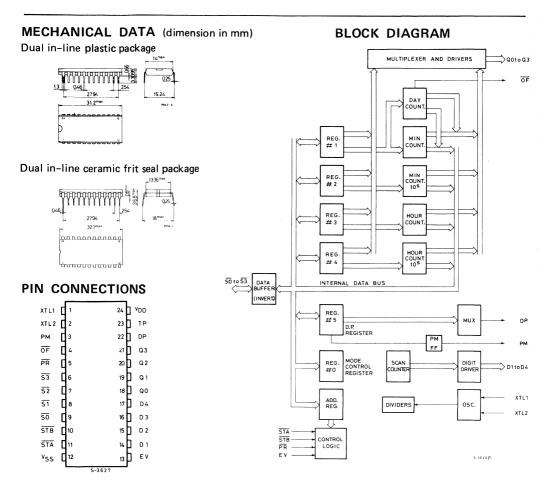

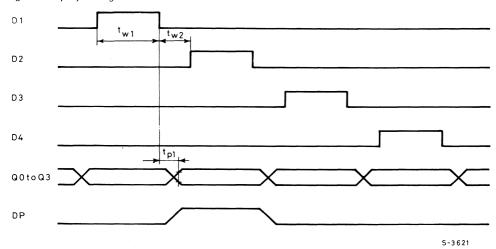

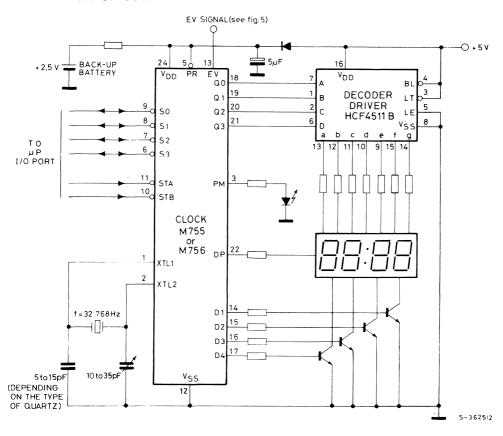

| M755       | COS/MOS       | Clock/display interface for microprocessors          | 177  |

| M756       | COS/MOS       | Clock/display interface for microprocessors          | 177  |

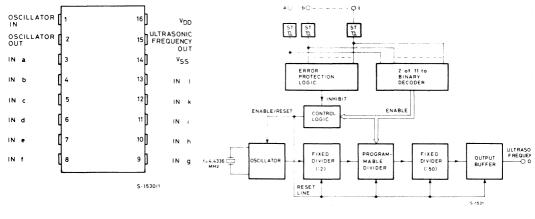

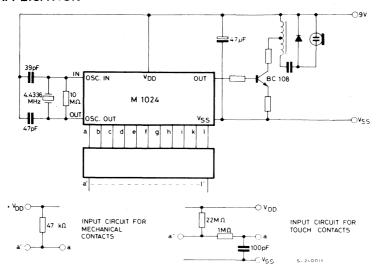

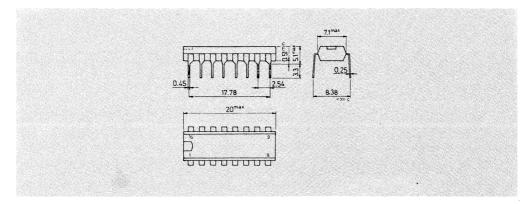

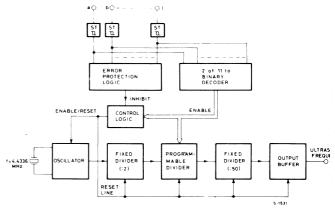

| M1024      | COS/MOS       | 30-channel remote control transmitter                | 215  |

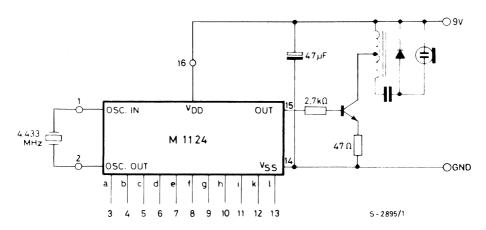

| M1124      | COS/MOS       | 30-channel remote control transmitter                | 219  |

| TELECOMMU  | INICATIONS    |                                                      |      |

| M089       | N channel MOS | 2v0 avacana int martuis                              |      |

| M090       | N channel MOS | 2x8 crosspoint matrix A-law single channel PCM CODEC | 19   |

| M099       | N channel MOS | 2x8 crosspoint matrix                                | 27   |

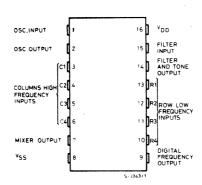

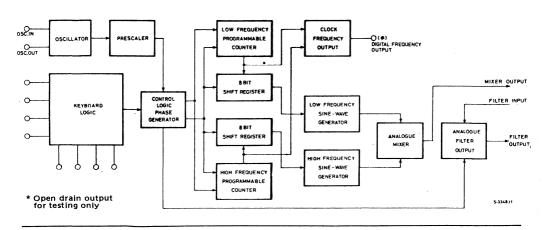

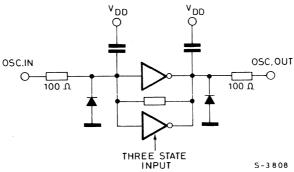

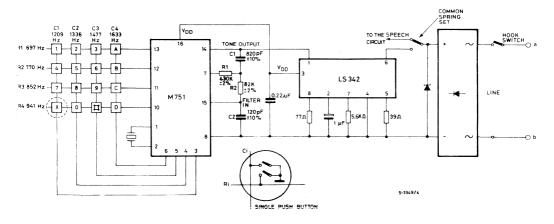

| M751       | COS/MOS       | Dual tone multifrequency generator                   | 19   |

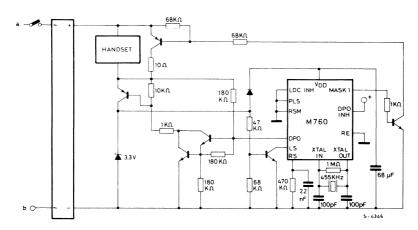

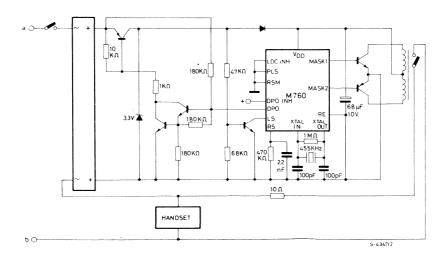

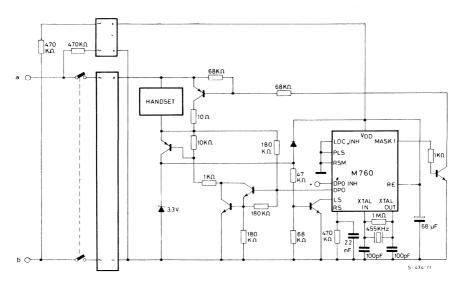

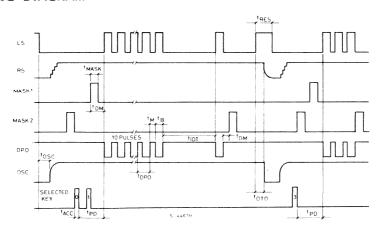

| M760/A     | COS/MOS       | Loop disconnect dialler                              | 159  |

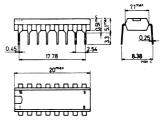

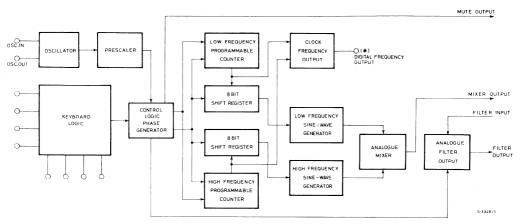

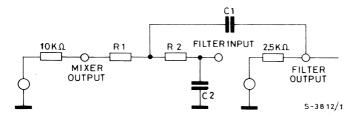

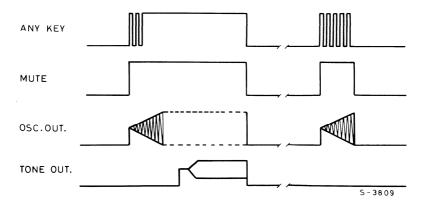

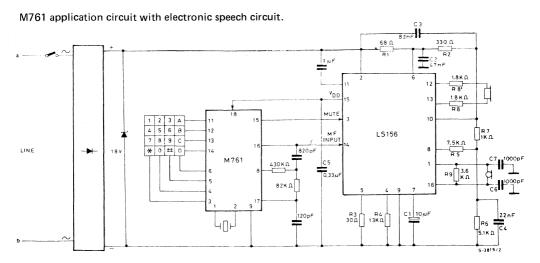

| M761/A     | COS/MOS       | Dual tone multifrequency generator                   | 185  |

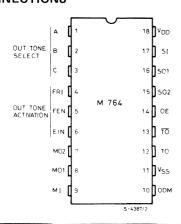

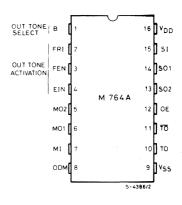

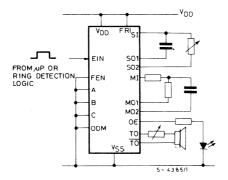

| M764/A     | COS/MOS       | Tone ringer                                          | 195  |

| M5156      | COS/MOS       | A-Law companding codec                               | 205  |

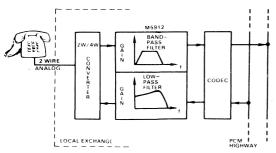

| M5912      | MOS           | PCM transmit/receive filters                         | 279  |

| M22100     | COS/MOS       |                                                      | 291  |

| IVIZZ 100  | COS/IVIOS     | 4x4 crosspoint switch with control memory            | 303  |

# FUNCTIONAL INDEX (continued)

| Type         | Technology    | Function                                                    | Page |

|--------------|---------------|-------------------------------------------------------------|------|

| MEMORIES     |               |                                                             |      |

| M120         | N channel MOS | 1024-bit non-volatile RAM                                   | 73   |

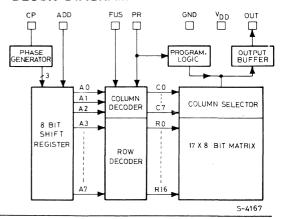

| M274-XCARD   | N channel MOS | Programmable electronic credit card                         | 125  |

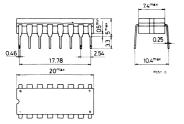

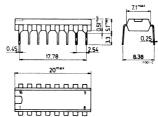

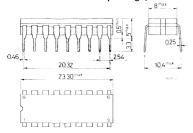

| M2102A/AL    | N channel MOS | 1024-bit static RAM                                         | 223  |

| M2114        | N channel MOS | 1024 x 4-bit static RAM                                     | 229  |

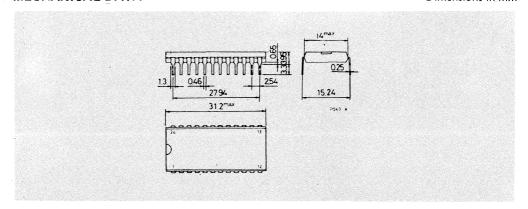

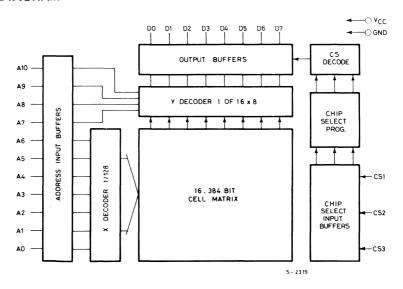

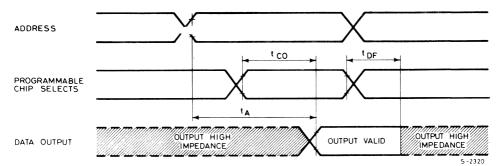

| M2316E       | N channel MOS | 16384-bit read only memory                                  | 233  |

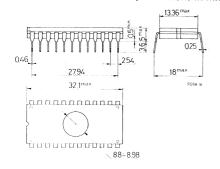

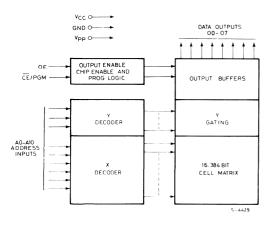

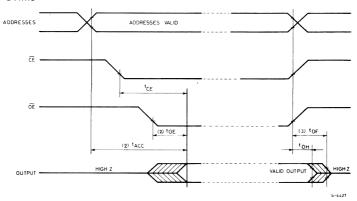

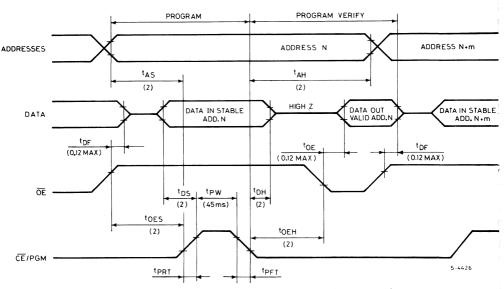

| M2716        | N channel MOS | 16384-bit UV Erasable Prom.                                 | 237  |

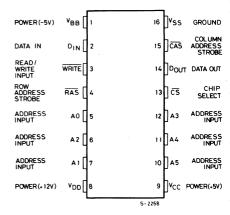

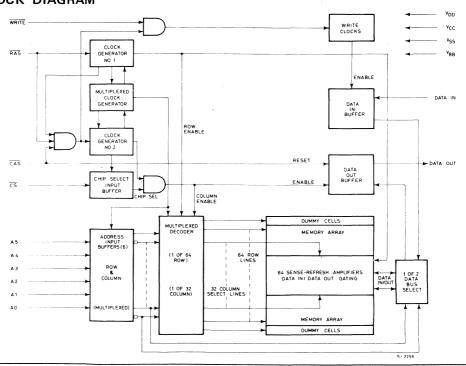

| M4015        | N channel MOS | 4096-bit dynamic RAM                                        | 245  |

| M4027        | N channel MOS | 4096-bit dynamic RAM                                        | 251  |

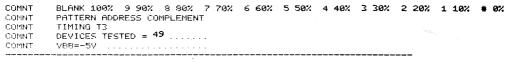

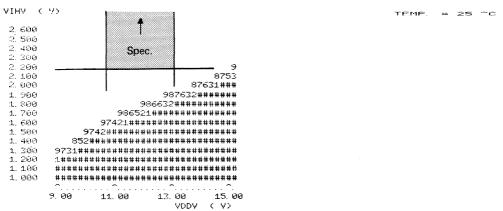

| M4116        | N channel MOS | 16384-bit dynamic RAM                                       | 263  |

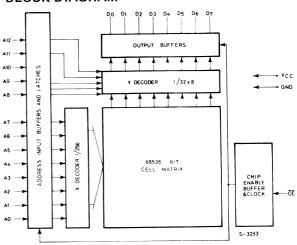

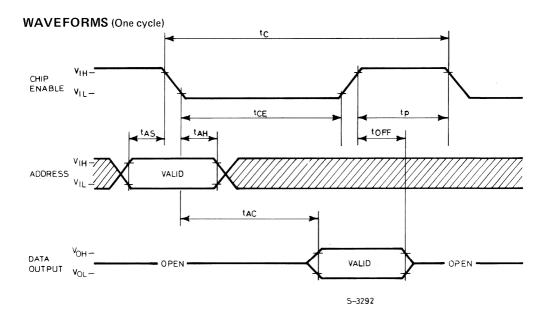

| M36000       | N channel MOS | 64K-bit read only memory                                    | 307  |

|              |               |                                                             |      |

|              |               |                                                             |      |

| CLOCKS & TIN |               |                                                             | 404  |

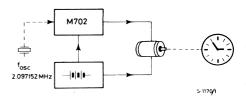

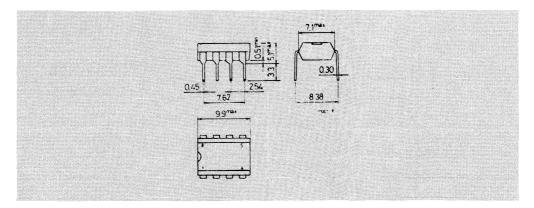

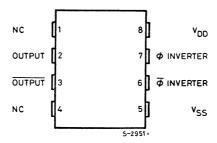

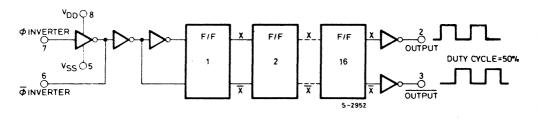

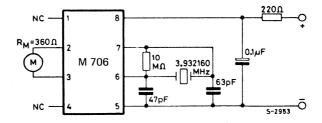

| M702         | COS/MOS       | 16-stage counter                                            | 131  |

| M706         | COS/MOS       | 16-stage counter                                            | 135  |

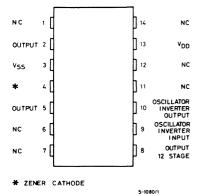

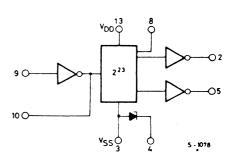

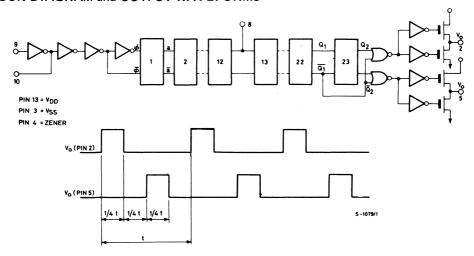

| M714         | COS/MOS       | 23-stage counter                                            | 139  |

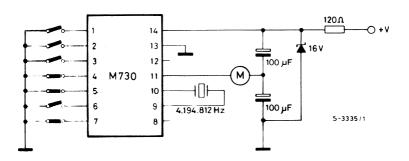

| M730         | COS/MOS       | 23-stage counter                                            | 143  |

| M731         | COS/MOS       | 16-stage counter                                            | 147  |

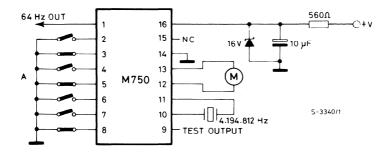

| M750         | COS/MOS       | 23-stage counter with intermediate output at the 16th stage | 155  |

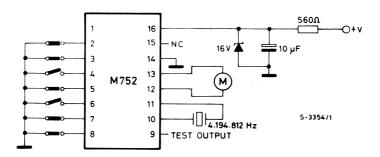

| M752         | COS/MOS       | 16-stage counter                                            | 169  |

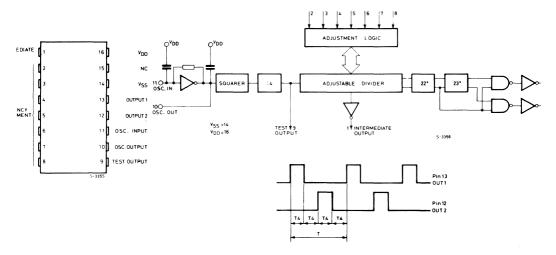

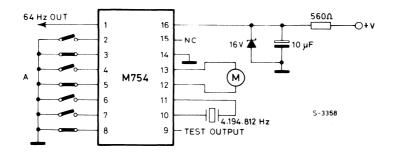

| M754         | COS/MOS       | 23-stage counter with intermediate output at the 16th stage | 173  |

|              |               |                                                             |      |

| SHIFT REGIS  | TERS          |                                                             |      |

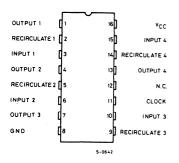

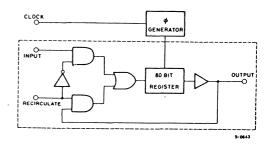

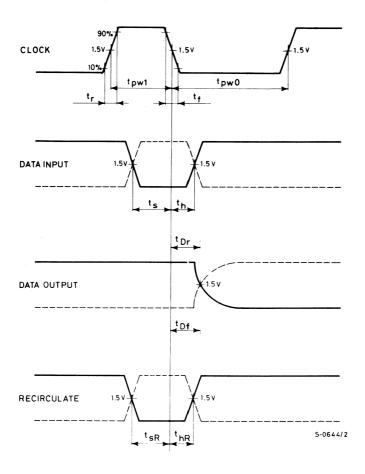

| M142/A       | N channel MOS | Quad 80-bit static shift register                           | 79   |

|              |               |                                                             |      |

#### MOS PROCESSES AND PRODUCTS

N-channel is the major MOS process at SGS. This process was developed independantly and has significant advantages, but it remains compatible for production of true second source products. Current production uses 5  $\mu$ m and 4  $\mu$ m features for products such as the M3870, Z8, Z80 and Z8000 microprocessors, 16K and 64K ROMs.

The SGS NV-RAM (Non-volatile memory) process which is compatible with the N-channel process allows integration of non-volatile memory blocks on the same chip as other random logic. This NV-RAM process provides better reliability than competitive MNOS products and an extrapolated data retention of over 100 years. Products using this compatible process include the M120 256x4 non-volatile RAM, the 16 and 32 channel Electronic Program Memories for voltage synthesised TV tuning, a new Phase Locked Loop and 32 word x 16 bit NV-RAM tuning circuit and the XCARD electronic credit card: this type of electronic credit card is forecast to replace existing magnetic cards and open up new markets in credit based POS applications.

#### THE TECHNOLOGY

Circuit design and layout on graphic terminals includes direct on-screen design for LSI products, advanced design rule check and process electrical layout check. Master mask production from the computer tapes is by automated electron beam exposure which eliminates the step-and-repeat mask production stage. Projection lithography machines are used for wafer exposure to extend working mask life and reduce defects. Ion implant, is used extensively for deposition and an Arsenic ion implant is planned for high speed circuits.

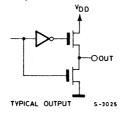

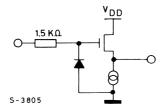

#### LOW VOLTAGE AND HIGH DENSITY CMOS

Three advanced technologies are in production at SGS: a Low Voltage Aluminium Gate process used for telephone MF and loop disconnect diallers, a High Density silicon gate process used for CODEC and TV remote control products and a High Density Low Voltage silicon gate process, operating on 1.5–2V supplies, aimed at pacemakers, microprocessors etc. The HD CMOS process, using a 4  $\mu$ m technology increases random logic gate density by a factor of 4 and gives a 0.1 pJ power/speed performance which exceeds that of HMOS 2 $\mu$ m devices.

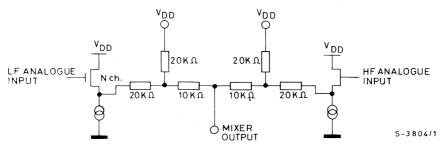

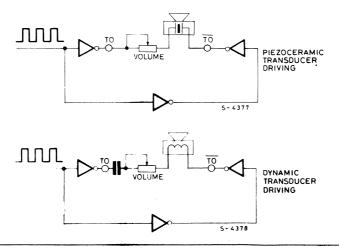

#### TELECOMMUNICATIONS CMOS

CMOS is a major technology for Telecommunications products. The speed/performance of High Density circuits closely matches the applications such as telephone diallers, tone ringers, CODEC's and cross point switches. The digital filters and analogue circuits integrated on the Multifrequency Tone Dialler chips provide a clean tone output meeting worldwide specifications. The low power consumption and high output drive allows a tone ringer to drive a transducer directly from the telephone line, the circuit uses a digital filter to detect the ringing tone from the line. The CMOS CODEC circuits integrate both analogue and digital blocks of the CODEC function and use little power.

#### SGS-ATES MOS PROCESSES

- 1. Low threshold N-channel enhancement/depletion mode with an N-type polycrystalline silicon gate

- Threshold voltage: 0.6 to 1.2V

- Supply voltage: V<sub>CC</sub>= +5V

- Used in static and dynamic systems (Z80/M3870/M36000)

- Compatible with bipolar circuits

- 2. N-channel enhancement/depletion mode with an N-type polycrystalline silicon gate

- Threshold voltage: 0.8 to 1.2V

- Supply voltages: V<sub>DD</sub>= +12V, V<sub>CC</sub>= 5V

- Used in static and dynamic systems

- Compatible with bipolar circuits

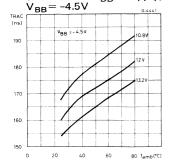

- 3. N-channel enhancement/depletion mode with double N-type polycrystalline silicon gate

- Threshold voltage: 0.8 to 1.2V with  $V_{BB}\!\!=\!$  -5V

- Supply voltages:  $V_{DD}$ = +12V,  $V_{BB}$ = -5V,  $V_{CC}$ = 5V

- Used for dynamic RAMs

- Compatible with bipolar circuits

- 4. N-channel enhancement/depletion mode with double N-type polycrystalline silicon gate

- Threshold voltage: 0.8 to 1.2V

- Supply voltage: V<sub>CC</sub> = 5V

- Used for UV erasable and electrically programmable ROMs (M2716)

- Compatible with bipolar circuits

- 5. N-channel enhancement/depletion mode with double N-type polycrystalline silicon gate

- Threshold voltage: 0.8V to 1.2V

- Supply voltages: V<sub>DD</sub> = +12V, V<sub>CC</sub> = +5V

- Used for NON VOLATILE RAMs (M120/M193/M293)

- Compatible with bipolar circuits

- 6. COS/MOS Aluminum Gate A & B process

- Threshold voltage: 1 to 2V

- Supply voltage: V<sub>DD</sub> = +3 to +18V

- 7. COS/MOS Aluminum Gate low threshold voltage

- Threshold voltage: 0.5V to 1V

- Supply voltage: V<sub>DD</sub> = 1.5 to 5V

- 8. COS/MOS Silicon Gate High Density

- Threshold voltage: 0.8V to 1.2V

- Supply voltages: V<sub>DD</sub>=+3 to 12V

| DATA-SHEETS |  |  |

|-------------|--|--|

|             |  |  |

|             |  |  |

# MOS INTEGRATED CIRCUITS

#### 1 OF 16 DECODER

- SPECIFICALLY DESIGNED FOR TV APPLICATION

- MINIMIZATION OF THE EXTERNAL COMPONENTS

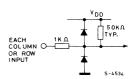

- INTERNAL PULL-UP FOR USE WITH LIGHT PRESSURE SWITCHES (M054)

- OPEN DRAIN OUTPUTS FOR TOUCH CONTROL (M055)

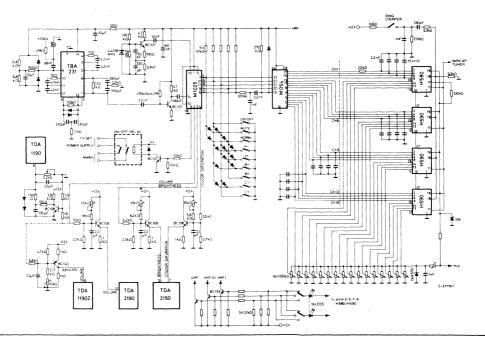

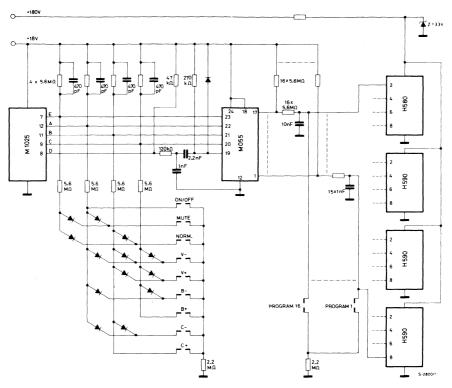

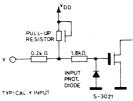

The M 054, M 055 are monolithic integrated circuits specifically designed to act as interface between M 1025 (30 channel ultrasonic receiver) and H 580/590 (quad analog switch) in TV applications. The inputs A,B,C,D,E are driven directly from the corresponding outputs of the M 1025. If G input is high the circuits decode the binary combinations from 0 to 15, if G is low the combinations from 16 to 31 are decoded instead. The M 054 has an internal pull-up circuit on the outputs to minimize the number of external components when light pressure switches are used. The M 055 has open drain outputs for touch control applications. The circuits are constructed with N-channel silicon gate technology and are supplied in a 24-lead dual in-line plastic package.

#### ABSOLUTE MAXIMUM RATINGS\*

| V <sub>DD</sub> **   | Supply voltage                        | -0.5 to 20 | V  |

|----------------------|---------------------------------------|------------|----|

| V                    | Input voltage                         | -0.5 to 20 | V  |

| V <sub>O (off)</sub> | Off state output voltage (M 055 type) | 20         | V  |

| P <sub>tot</sub>     | Total power dissipation               | 1          | W  |

| Tstq                 | Storage temperature                   | -65 to 150 | °C |

| Top                  | Operating temperature                 | 0 to 70    | °C |

<sup>\*</sup> Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other condition above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

**ORDERING NUMBERS: M 054 B1**

M 055 B1

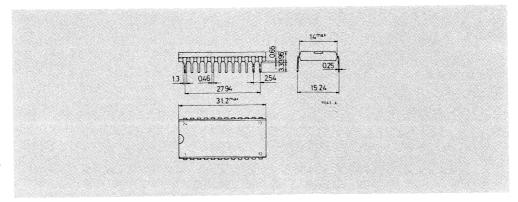

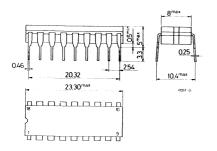

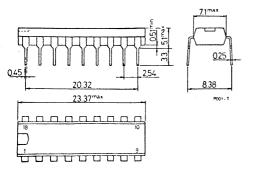

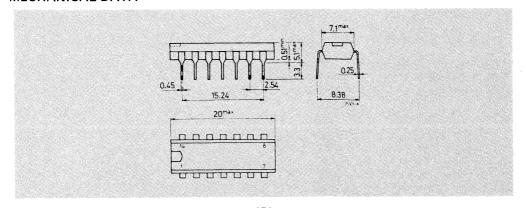

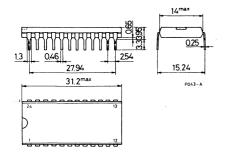

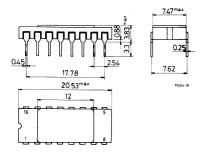

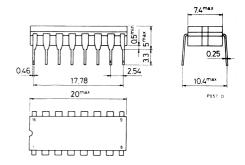

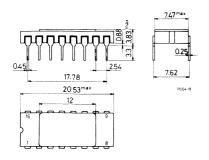

#### MECHANICAL DATA

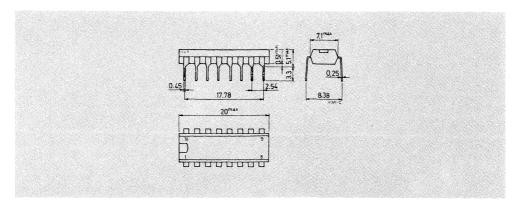

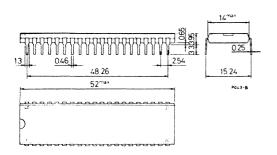

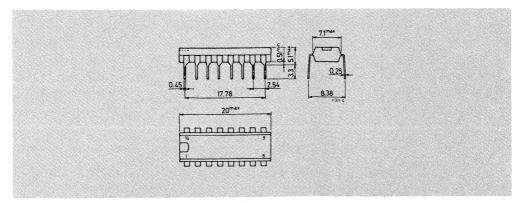

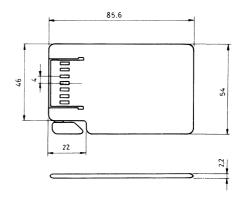

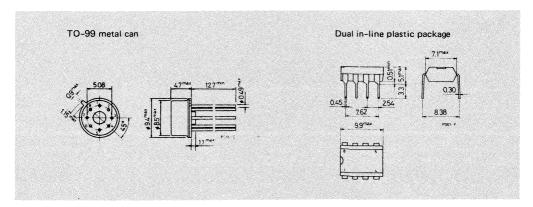

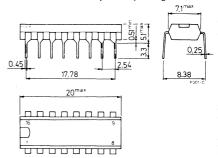

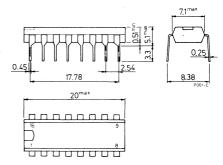

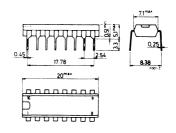

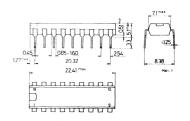

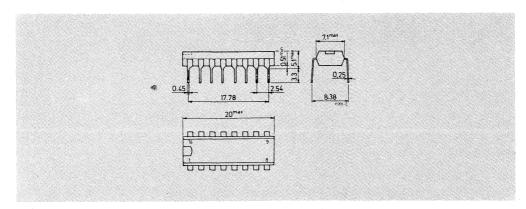

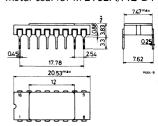

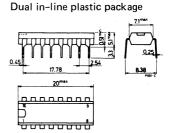

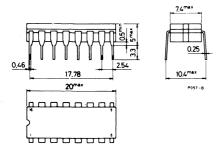

Dimensions in mm

<sup>\*\*</sup> All voltages values are referred to V<sub>SS</sub> pin voltage.

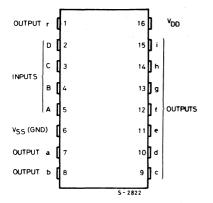

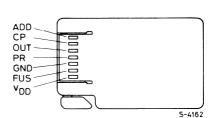

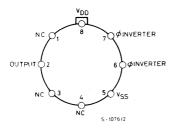

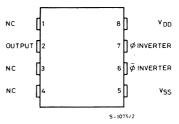

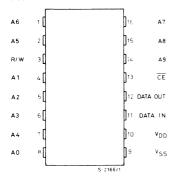

# PIN CONNECTIONS

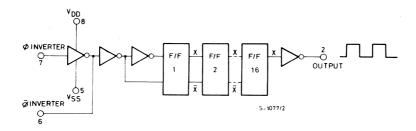

# **BLOCK DIAGRAM**

# TRUTH TABLE (positive logic)

| INPUTS M 1025 output code                           | OUTPUTS                                |

|-----------------------------------------------------|----------------------------------------|

| E A B C D G                                         | 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 |

| 0 0 0 0 0 1 1 0 0 0 0 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 | 0                                      |

#### RECOMMENDED OPERATING CONDITIONS

| $V_{DD}$        | Supply voltage                       | 17 to 19             |    |

|-----------------|--------------------------------------|----------------------|----|

| $V_1$           | Input voltage                        | 0 to V <sub>DD</sub> | V  |

| $V_{O(off)}$    | Off state output voltage (M055 type) | 19                   | V  |

| T <sub>op</sub> | Operating temperature                | 0 to 70              | °C |

# STATIC ELECTRICAL CHARACTERISTICS (over recommended operating conditions)

|                     |                       |                   | T                                       | onditions                                     | Val                 | ues at 2 | 5° C            | Unit  |

|---------------------|-----------------------|-------------------|-----------------------------------------|-----------------------------------------------|---------------------|----------|-----------------|-------|

|                     | Parameter             | •                 | l est co                                | martions                                      | Min.                | Тур.     | Max.            | Oiiit |

| VIH                 | High level input      | A-B-C-D-E Inputs  |                                         |                                               | ۷ <sub>D,D</sub> -1 |          | V <sub>DD</sub> | ·V    |

|                     | voltage               | G Input           |                                         |                                               | 3                   |          | $V_{DD}$        | Ľ     |

| VIL                 | Low level input       | A-B-C-D-E Inputs  |                                         |                                               | 0                   |          | $V_{DD}$ -4     | V     |

| 1                   | voltage               | G Input           | 1                                       |                                               | 0                   |          | 0.3             | ľ     |

| loL                 | Low level output cur  | rent              | V <sub>DD</sub> = 17V                   | V <sub>OL</sub> = 0.4V                        | 1.6                 |          |                 | mΑ    |

| Іон                 | High level output cur | rent (M 055 Type) | M 054 Type                              | V <sub>DD</sub> = 19V<br>V <sub>OH</sub> = 8V |                     |          | -200            | μА    |

| I <sub>O(off)</sub> | Off state output curr | ent (M 054 Type)  | M 055 Type<br>V <sub>DD</sub> = 19V     | V <sub>O(off)</sub> = 8V                      |                     |          | 1               | μΑ    |

| lDD                 | Supply current        |                   | V <sub>DD</sub> = 19V<br>All input to V | SS                                            |                     |          | 25              | mΑ    |

# TYPICAL APPLICATIONS

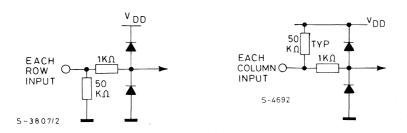

Fig. 1 and 2 show a typical application of M 054 and M 055 respectively in a TV remote control system.

Fig. 1 - M054 with light pressure switches

# TYPICAL APPLICATIONS (continued)

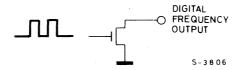

Fig. 2 - M055 with direct touch controls

#### PRELIMINARY DATA

#### TONE GENERATOR

- SINGLE POWER SUPPLY

- WIDE SUPPLY VOLTAGE OPERATING RANGE

- LOW POWER DISSIPATION < 500 mW</li>

- 13 (M082/A, M083/A) OR 12 (M086/A) TONE OUTPUTS

- HIGH OUTPUT DRIVE CAPABILITY

- HIGH ACCURACY OF OUTPUT FREQUENCIES: ERROR LESS THAN ± 0.069%

- INPUT PROTECTED AGAINST STATIC CHARGES

- LOW INTERMODULATION

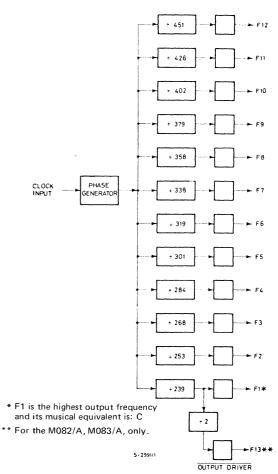

The M082/A, M083/A and M086/A are monolithic tone generators specifically designed for electronic organs. The only difference between the M082, M083, M086 and the M082A, M083A, M086A is the maximum input clock frequency, which is 4500 KHz for the standard types and 2500 KHz for the "A" types. Constructed on a single chip using low threshold N-channel silicon gate technology they are supplied in a 16 lead dual in-line plastic package.

#### **ABSOLUTE MAXIMUM RATINGS\***

| $V_{i}$          | Voltage on any pin relative to V <sub>SS</sub> (GND) | +20 to -0.3 | V  |

|------------------|------------------------------------------------------|-------------|----|

| Top              | Operating temperature                                | 0 to 50     | °C |

| T <sub>stg</sub> | Storage temperature                                  | -65 to 150  | °C |

<sup>\*</sup> Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other condition above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

ORDERING NUMBERS: M082B1 M082A B1

M083B1 M083A B1

M086B1 M086A B1

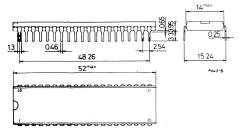

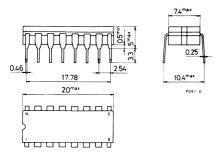

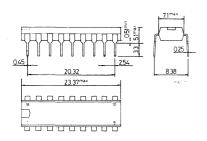

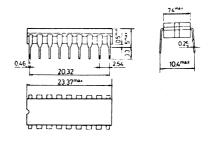

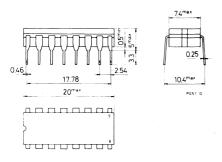

#### **MECHANICAL DATA**

Dimensions in mm

#### PIN CONNECTIONS

- \* V<sub>DD</sub> is the highest supply voltage

- \*\* V<sub>SS</sub> is the lowest supply voltage

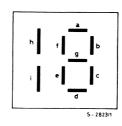

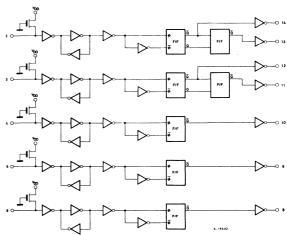

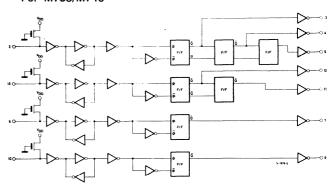

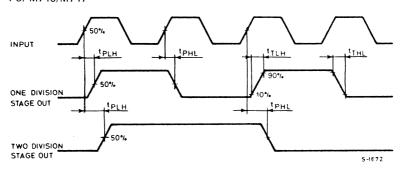

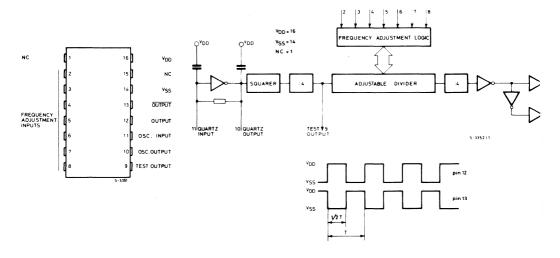

#### **BLOCK DIAGRAM**

# RECOMMENDED OPERATING CONDITIONS

|                 | Parameter              | Test conditions |      | Values |      | Unit  |

|-----------------|------------------------|-----------------|------|--------|------|-------|

|                 | rarameter              | rest conditions | Min. | Тур.   | Max. | Oiiit |

| V <sub>SS</sub> | Lowest supply voltage  |                 | 0    |        | 0    | V     |

| V <sub>DD</sub> | Highest supply voltage |                 | +10  | +12    | +14  | >     |

# **ELECTRICAL CHARACTERISTICS** (0°C $\leq$ T<sub>amb</sub> $\leq$ 50°C; V<sub>SS</sub>=0V; V<sub>DD</sub>=+10V to+14V unless otherwise specified)

| Parameter                         |                                               |                     | Values               |         |                    |      |      |

|-----------------------------------|-----------------------------------------------|---------------------|----------------------|---------|--------------------|------|------|

|                                   |                                               | Test conditions     | Min.                 | Тур.    | Max.               | Unit | Fig. |

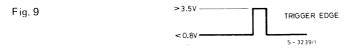

| VIL                               | Input clock, low                              |                     | V <sub>SS</sub>      |         | V <sub>SS</sub> +1 | V.   | 1    |

| VIH                               | Input clock, high                             |                     | V <sub>DD</sub> -1   |         | V <sub>DD</sub>    | V    |      |

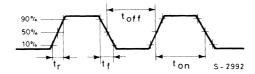

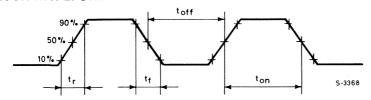

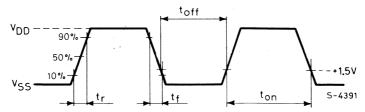

| t <sub>r</sub> , t <sub>f</sub>   | Input clock rise and fall times<br>10% to 90% | 4.5 MHz             |                      |         | 30                 | ns   | 1    |

| ton, toff                         | Input clock on and off times                  | 4.5 MHz             |                      | 111     |                    | ns   | 1    |

| Cı                                | Input capacitance                             |                     |                      | 5       | 10                 | pF   |      |

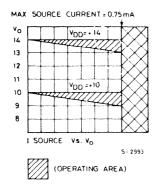

| V <sub>OH</sub>                   | Output high                                   | 0.75 mA             | V <sub>DD</sub> -1.5 |         | $V_{DD}$           | V    | 2    |

| VOL                               | Output low                                    | 0.70 mA             | V <sub>SS</sub>      |         | V <sub>SS</sub> +1 | V    | 2    |

| t <sub>ro</sub> , t <sub>fo</sub> | Qutput rise and fall times<br>500 pF load     |                     | 250                  |         | 2500               | ns   | 3    |

| ton, toff                         | Output duty cycle                             | M 082               |                      | 30      |                    | %    |      |

|                                   |                                               | M 083, M 086        |                      | 50      |                    | 70   |      |

| I <sub>DD</sub>                   | Supply current                                |                     |                      | 24      | 35                 | mA . | *    |

| f <sub>1</sub>                    | Input clock frequency                         | M082, M083, M086    | 100                  | 4000.48 | 4500               | kHz  |      |

| f,                                | Input clock frequency                         | M082A, M083A, M086A | 100                  | 2000.24 | 2500               | kHz  |      |

<sup>\*</sup> Output unloaded.

Fig. 1 Input clock waveform

Fig. 2 - Output signal d.c. loading

Fig. 3 - Output loading

# MOS INTEGRATED CIRCUITS

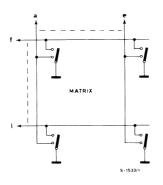

#### 2 x 8 CROSSPOINT MATRIX

- VERY LOW ON RESISTANCE

- HIGH CROSS-TALK AND OFF-STATE ISOLATION

- SERIAL SWITCH ADDRESSING, μ-PROCESSOR COMPATIBLE

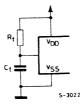

The M089 and M099 are 2x8 crosspoint matrices consisting of 16 N-channel MOS transistors. Both devices are similar in operation, the only difference being that in the M099 the "all switches reset" function is implemented by a microprocessor command.

Both devices have been specially designed to provide switches with low cross-talk, high off-state isolation (both better than -90 dB) and low on-resistance.

#### **ABSOLUTE MAXIMUM RATINGS\***

| ~                  |                                                     |            |    |

|--------------------|-----------------------------------------------------|------------|----|

| V <sub>DD</sub> ** | Supply voltage                                      | -0.5 to 17 | V  |

| V                  | Input voltage pins 4, 5, 12, 13                     | -0.5 to 17 | V  |

| VIN-VOUT           | Differential voltage across any disconnected switch | 10         | V  |

| $P_{tot}$          | Total power dissipation                             | 640        | mW |

| Top                | Operating temperature range: for plastic            | 0 to 70    | °C |

|                    | for ceramic                                         | -40 to 70  | °C |

| $T_{stg}$          | Storage temperature range                           | -65 to 150 | °C |

|                    |                                                     |            |    |

<sup>\*</sup> Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other condition above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### ORDERING NUMBERS:

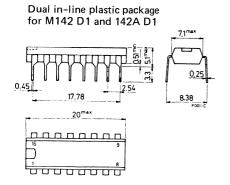

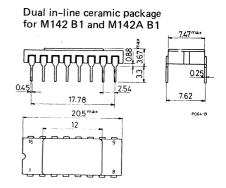

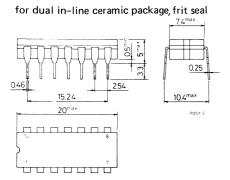

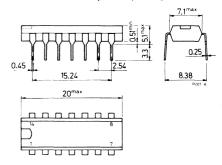

M089/M099 B1 for dual-in-line plastic package M089/M099 D1 for dual-in-line ceramic package

M089/M099 F1 for dual-in-line ceramic package, frit seal

<sup>\*\*</sup> With respect to V<sub>SS</sub> (GND) pin.

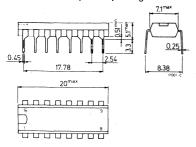

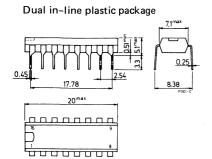

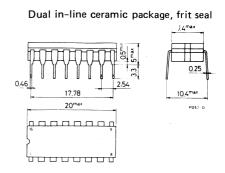

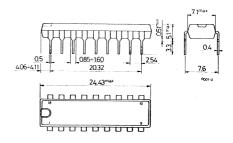

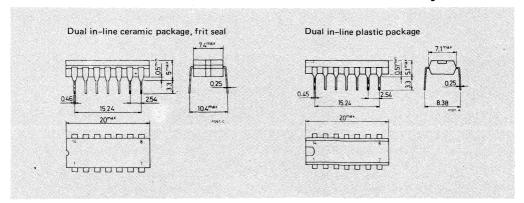

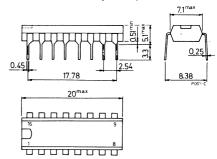

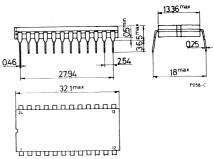

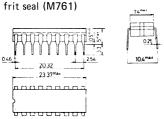

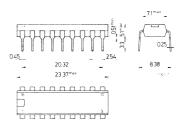

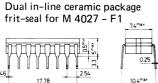

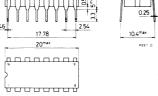

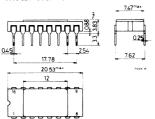

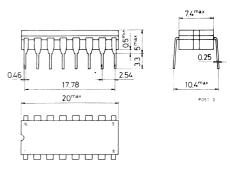

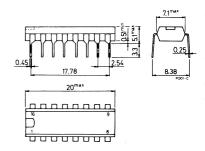

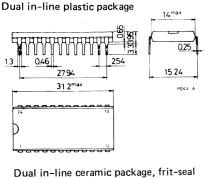

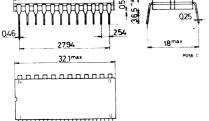

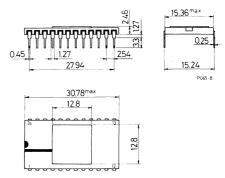

#### MECHANICAL DATA (dimensions in mm)

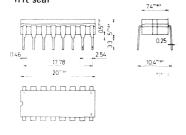

#### Dual-in-line plastic package

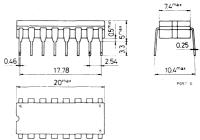

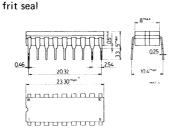

# Dual-in-line ceramic package frit seal

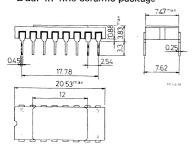

#### Dual-in-line ceramic package

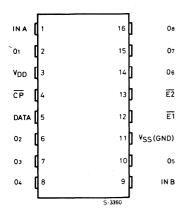

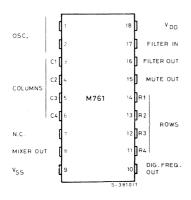

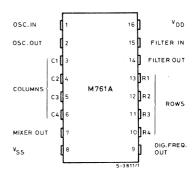

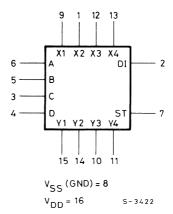

#### PIN CONNECTIONS

# LOGIC DIAGRAM

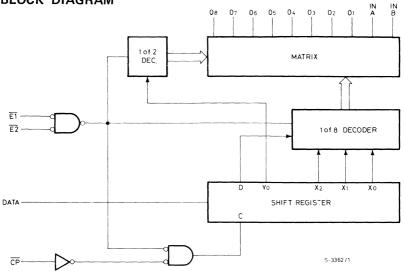

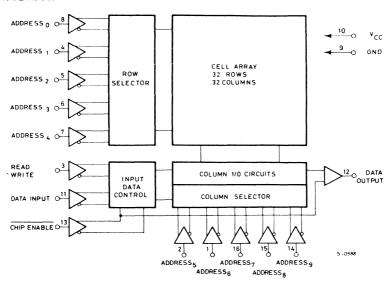

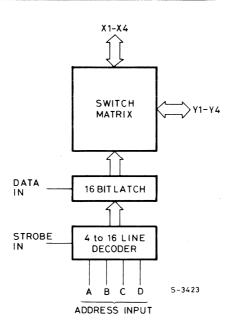

# M089 BLOCK DIAGRAM

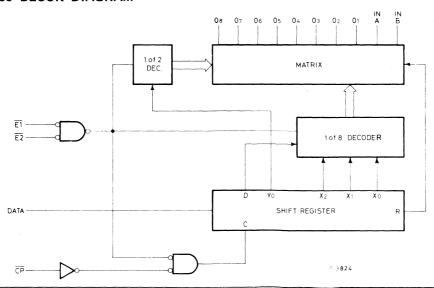

# M099 BLOCK DIAGRAM

#### CIRCUIT DESCRIPTION

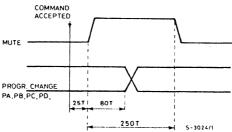

The M089 and M099 are capable of forming any combination of switch conditions in an 8x2 matrix. Each switch is individually set and a latch maintains it in its set condition.

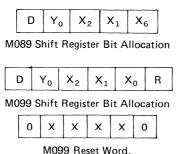

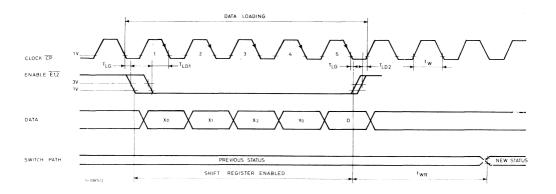

The switch address and control bits are loaded serially into an internal shift register (5 bit for M089, 6 bit for M099) when inputs  $E_1$ , and  $E_2$  are low. The address bits in both matrices consist of: 3 input selection bits  $(X_0-X_2)$  and a single output selection bit  $(Y_0)$ . A fifth (control) bit (D) defines whether the chosen switch is to be opened or closed.

In the M099 a sixth bit (R) is an "all switch reset". Reset occurs on the low to high transition of the enable inputs when both D and R are zero.

During normal selection the R bit must be a 1.

high transition of one or both enable inputs.

Data bits are clocked into the shift register on the high to low transition of the clock input (CP). If more than 5 (or 6 in the case of the M090) clock transmission are applied during loading of the shift register the last 5 (or 6) data bits are loaded into it. The status of the switch addressed changes on the low to

# ENABLE INPUTS TRUTH TABLE

| Ē1 | Ē₂ | FUNCTION            |                                    |  |  |

|----|----|---------------------|------------------------------------|--|--|

| E1 | E2 | M089                | М099                               |  |  |

| L  | L  | Data Load           |                                    |  |  |

|    | L  |                     | addressed                          |  |  |

| L  |    | addressed<br>switch | switch<br>changed or<br>all switch |  |  |

|    |    | changed             | reset                              |  |  |

#### DATA BIT TRUTH TABLE

| – M089 <b>–</b> |                                       |  |  |  |  |

|-----------------|---------------------------------------|--|--|--|--|

| Data            | Switch status after enable transition |  |  |  |  |

| L               | disconnect                            |  |  |  |  |

| Н               | connect                               |  |  |  |  |

#### DATA AND RESET BIT TRUTH TABLE

|   | – M099 only –     |                               |  |  |  |  |  |

|---|-------------------|-------------------------------|--|--|--|--|--|

| D | D R Switch status |                               |  |  |  |  |  |

| L | L                 | all switches reset            |  |  |  |  |  |

| н | L                 | no change                     |  |  |  |  |  |

| L | н                 | addressed switch disconnected |  |  |  |  |  |

| Н | Н                 | addressed switch connected    |  |  |  |  |  |

#### DATA BITS TRUTH TABLE FOR SWITCH SELECTION

|      | O <sub>1</sub><br>Y <sub>0</sub> X <sub>2</sub> X <sub>1</sub> X <sub>0</sub> | 02   | 03   | 04   | 05   | 06   | 07   | 08   |

|------|-------------------------------------------------------------------------------|------|------|------|------|------|------|------|

| IN A | 1111                                                                          | 1011 | 1101 | 1001 | 1110 | 1010 | 1100 | 1000 |

| IN B | 0111                                                                          | 0011 | 0101 | 0001 | 0110 | 0010 | 0100 | 0000 |

For example to address the switch connecting IN A to  ${\rm O}_5$  the shift register must be loaded with the code:

|               | M089                                                          | M099                                                            |

|---------------|---------------------------------------------------------------|-----------------------------------------------------------------|

|               | р Y <sub>0</sub> X <sub>2</sub> X <sub>1</sub> X <sub>0</sub> | D Y <sub>0</sub> X <sub>2</sub> X <sub>1</sub> X <sub>0</sub> R |

| to connect    | 11110                                                         | 111101                                                          |

| to disconnect | 01110                                                         | 011101                                                          |

# **ELECTRICAL CHARACTERISTICS** ( $T_{amb}=0$ to $70^{\circ}C$ for M089/M099 B1; -40 to $70^{\circ}C$ for M089/M099 F1, D1; $V_{DD}=14V$ to 16V unless otherwise specified)

| Parameter         |                                          | Test conditions           | Min.                                                                                                        | Тур. | Max. | Unit            |     |

|-------------------|------------------------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------|------|------|-----------------|-----|

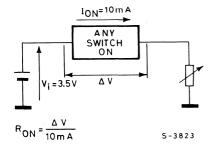

| R <sub>ON</sub> * |                                          |                           | T <sub>amb</sub> = 25°C<br>V <sub>i</sub> (A, B)= 3.5V<br>V <sub>DD</sub> = 14V I <sub>D(min)</sub> = 10 mA |      | 10   | 15              | Ω   |

| ∆R <sub>ON</sub>  | ON-resistance variat<br>any package      | tion in                   | T <sub>amb</sub> = 25°C<br>V <sub>i</sub> = 3.5V<br>V <sub>DD</sub> = 14V<br>I <sub>D</sub> = 10 mA         |      |      | ± 2             | %   |

| I <sub>DD</sub>   | Supply current                           |                           |                                                                                                             |      |      | 7               | mA  |

| ILI               | Input leakage                            | pins 4, 5<br>12, 13       | V <sub>i</sub> = 5V                                                                                         |      |      | 1               | μА  |

|                   |                                          | pins 1, 9                 | V <sub>iA</sub> , V <sub>iB</sub> = 4.5V<br>V <sub>O1</sub> , V <sub>O8</sub> = 1.5V                        |      |      | 0.2             | μΑ  |

|                   |                                          | pins 1, 9                 | V <sub>iA</sub> , V <sub>iB</sub> = 6V<br>V <sub>O1</sub> , V <sub>O8</sub> = 1.5V                          |      |      | 1               | μА  |

| l <sub>LO</sub>   | Output leakage                           | pins 2, 6, 7<br>8, 10, 14 | V <sub>O1</sub> , V <sub>O8</sub> = 4.5V<br>V <sub>iA</sub> , V <sub>iB</sub> = 1.5V                        |      |      | 0.2             | μА  |

|                   |                                          | 15, 16                    | V <sub>O1</sub> , V <sub>O8</sub> = 6V<br>V <sub>iA</sub> , V <sub>iB</sub> = 1.5V                          |      |      | 1               | μА  |

| $V_{low}$         | Logic 0 input level                      |                           | All inputs                                                                                                  | -0.3 |      | 0.8             | V   |

| V <sub>high</sub> | Logic 1 input level                      |                           | All inputs                                                                                                  | 4.5  |      | V <sub>DD</sub> | V   |

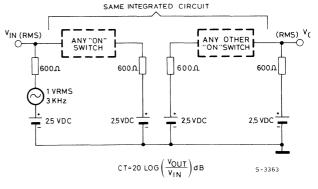

| СТ                | Cross-talk attenuati                     | on                        | See fig. 4                                                                                                  | 90   | 95   |                 | dB  |

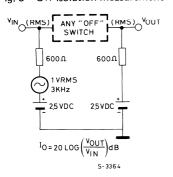

| Io                | Off isolation                            |                           | See fig. 5                                                                                                  | 90   | 95   |                 | dB  |

| fc∟               | Maximum clock inp                        | ut frequency              |                                                                                                             |      |      | 1               | MHz |

| T <sub>LG</sub>   | Lag time                                 |                           |                                                                                                             | 100  |      |                 | ns  |

| T <sub>LD1</sub>  | Lead time  Write time  Clock pulse width |                           | See fig. 6 for M089                                                                                         | 400  |      |                 |     |

| T <sub>LD2</sub>  |                                          |                           | See fig. 7 for M099                                                                                         | 150  |      |                 | ns  |

| T <sub>WR</sub>   |                                          |                           |                                                                                                             |      |      | 3               | μs  |

| tw                |                                          |                           | ]                                                                                                           | 0.4  |      | 100             | μs  |

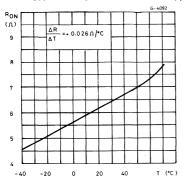

See fig. 1 and 2 for R<sub>ON</sub> variation with temperature and V<sub>BIAS</sub>.

Fig. 1 - R<sub>ON</sub> derating vs. temperature typ.

Fig. 2 - R<sub>ON</sub> derating vs. V<sub>BIAS</sub>.

R<sub>ON</sub>

(A)

20

16

12

10 VBIAS(V)

#### **TEST CIRCUITS**

Fig. 3 - R<sub>ON</sub> measurement

Fig. 4 - Crosstalk measurements

0

Fig. 5 - Off isolation measurement

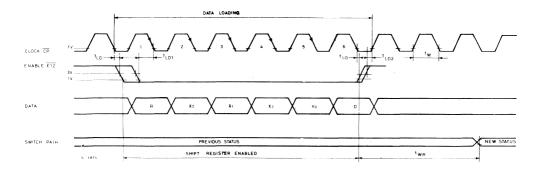

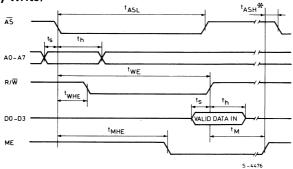

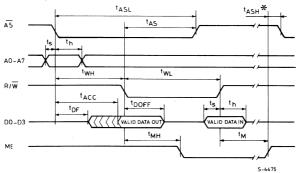

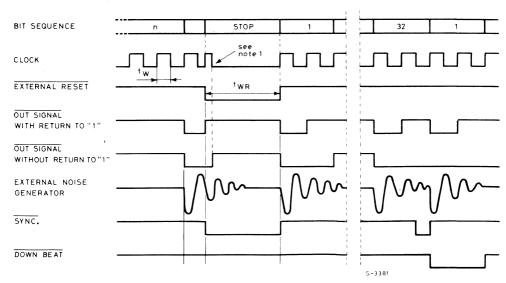

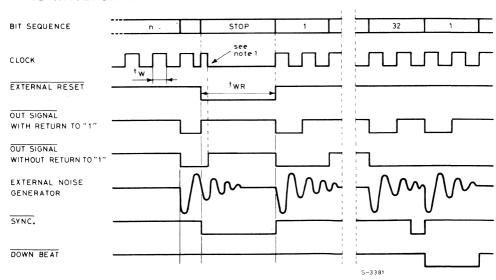

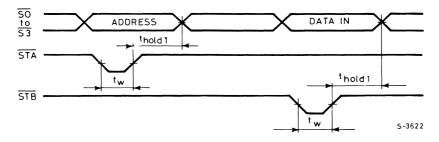

# TIMING DIAGRAMS

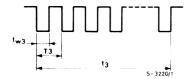

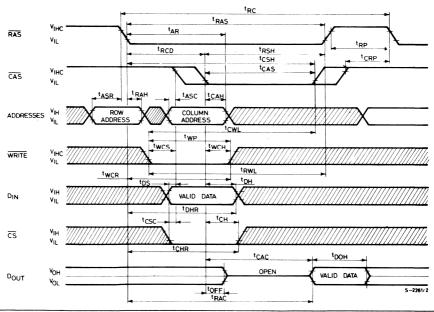

Fig. 6 - M089 timing diagram

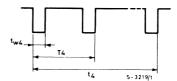

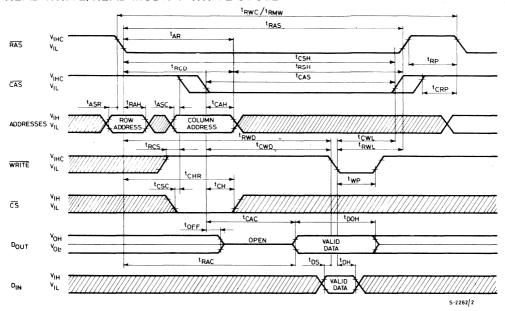

Fig. 7 - M099 timing diagram

#### ADVANCE DATA

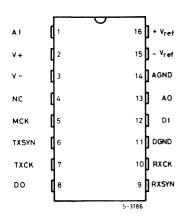

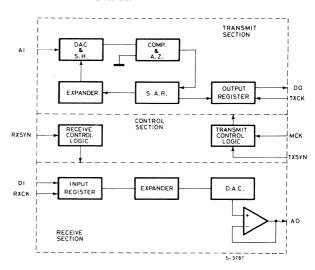

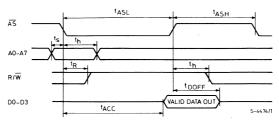

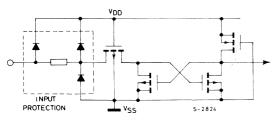

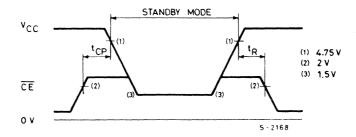

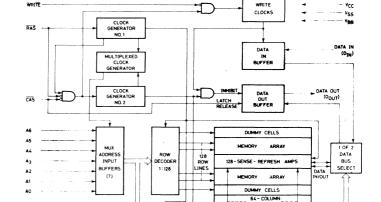

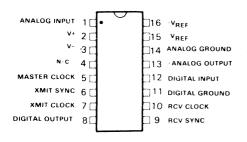

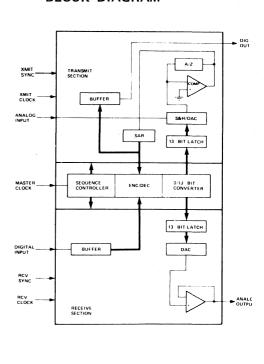

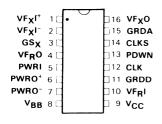

#### A - LAW SINGLE CHANNEL PCM CODEC

- ± 5V SUPPLY

- FOLLOWS CCITT A-LAW COMPANDING CODE

- EXCEEDS CCITT SPECIFICATIONS

- INDEPENDENT RECEIVE AND TRANSMIT SECTIONS

- FULLY ASYNCHRONOUS

- ON-CHIP AUTOZERO

- LOW EXTERNAL COMPONENT COUNT

- SEPARATE ANALOG AND DIGITAL GROUNDS

- SINGLE 16-PIN PACKAGE

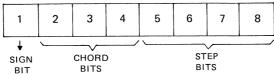

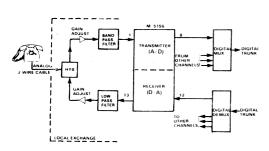

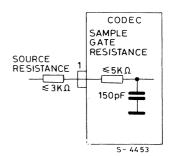

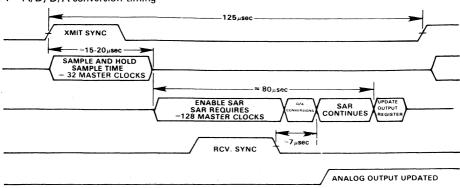

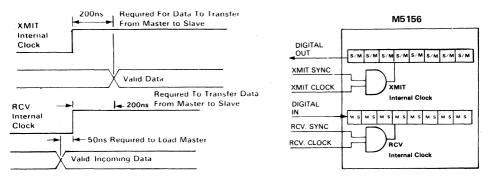

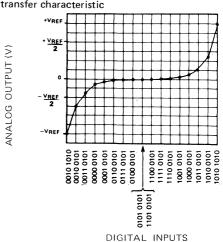

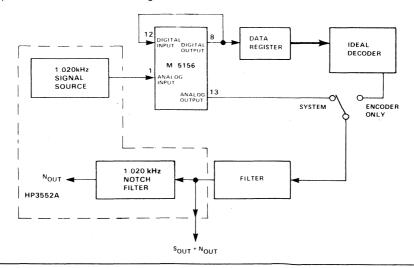

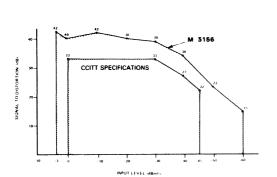

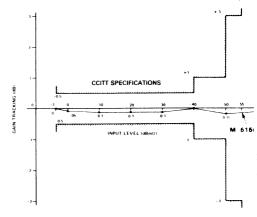

- TTL COMPATIBLE